High Bandwidth Flash:NANDはついにメモリのように振る舞えるのか?

AIインフラには、多くのシステムではまず表に出てこない限界を、はっきりあぶり出してしまうところがあります。

これまでの記事では、AIワークロード向けのHigh Bandwidth MemoryがどうやってGPUのすぐ近くにデータを置くのか、そしてDRAMとNANDの間にあるStorage Class Memoryが、アクティブメモリと従来型フラッシュストレージのあいだの溝をどう埋めるのかを見てきました。こうした層が存在するのは、システムが少しの待ち時間すら効率低下なしには受け入れられないからです。

ただ、業界が進もうとしている方向はそれだけではありません。そしてそこでは、まったく新しい種類のメモリを導入しようとしているわけでもありません。

むしろ、すでに存在しているもの、つまりNANDフラッシュを、本来想定されていなかった役割へ押し上げようとしているのです。

そこで出てくるのが、High Bandwidth Flashという考え方です。

NANDがもともと解くように作られていなかった問題

NANDフラッシュは、昔からひとつのシンプルな考え方を中心に設計されてきました。大量のデータを効率よく保存し、必要になったときに取り出すという考え方です。

たいていのワークロードでは、そのモデルで十分うまく機能します。データはストレージにあり、システムがそれを要求し、SSDが十分な速度で返してくれるので、ほとんどの人は遅延を意識しません。

AIワークロードは、その前提を変えてしまいます。

たまに読み書きが発生するのではなく、こうしたシステムは常に並列でデータを引き込み続けます。しかも多くの場合は何千ものスレッドをまたいで動いており、データ供給のばらつきに対する許容度はきわめて低いのです。ここで問題になるのは、単純な速度だけではありません。計算側をフルに動かし続けられるだけの、安定したデータの流れを維持できるかどうかです。

そこで従来型のNANDの振る舞いが、限界を見せ始めます。

高性能なNVMeドライブであっても、深いキューと高いスループットを備えていても、前提としているのはあくまでバースト的なアクセスです。メモリのように途切れず流れ続けるアクセスを前提にしたモデルではありません。

すると問いはこうなります。NANDをストレージとして扱うのをやめ、メモリシステムの一部のように扱い始めたら、何が起こるのか。

「High Bandwidth Flash」が実際に意味しているもの

High Bandwidth Flashは、正式な標準でもなければ、単一の製品カテゴリでもありません。

どちらかといえば、これはアーキテクチャの方向性として理解するほうが正確で、そこがHigh Bandwidth Memoryとの違いでもあります。

High Bandwidth Memoryは、あくまでメモリです。つまりDRAMであり、プロセッサのすぐ近くに置かれることで、きわめて高速なアクセスを実現するよう設計されています。HBMの本質は近接性と低遅延にあります。データをできるだけ計算の近くへ寄せ、ほとんど瞬時にアクセスできるようにすることが目的です。

一方、High Bandwidth Flashが解こうとしているのは別の問題です。NANDはシステムの中でより遠くにあり、遅延も高い、という前提を受け入れたうえで、その距離の不利を感じにくくするほど大量のデータを並列に動かすことへ重点を置いています。

シンプルに言えば、HBMはメモリを近づけることで速くする話です。High Bandwidth Flashは、アクセスのされ方を変えることで、ストレージをより速く振る舞わせる話です。

この違いは重要です。ここでの目標は、NANDをDRAMに変えることではありません。従来のストレージではシステム全体が鈍ってしまうような場面で、NANDを役に立つものにすることです。

この変化は、メディアそのものよりも、システム全体のレベルで起きています。

従来のように1台のSSDがリクエストを処理するのではなく、多数のNANDチャネルが並列で動き、容量だけではなく同時実行性を重視したコントローラが使われ、PCIe Gen5やGen6のインターフェースを通るデータ経路はより広くなり、さらにソフトウェア層が要求前にデータを予測して先回りで配置するようになっています。

こうした変化をまとめて見れば、NAND固有の遅延そのものがなくなるわけではありませんが、その遅延がシステムのボトルネックになる場面はかなり減っていきます。

帯域幅を別の視点で考える

「高帯域」と聞くと、多くの人はまず生の速度を思い浮かべます。

けれどもこの文脈でいう帯域幅は、どれだけ速いかというより、どれだけ多くのデータを同時に動かせるか、そしてその動きをどれだけ安定して維持できるかという意味合いが強いのです。

AIワークロードが必要としているのは、ただ速いアクセスではなく、大規模でも予測可能なアクセスです。

GPUクラスタが不均一にデータを引き込むと、ほんの小さな揺らぎでもシステムの一部が止まり得ます。それが何百、何千というノードに広がれば、無視できない非効率として表面化してきます。

High Bandwidth Flashは、その問題をならそうとする試みです。NANDの性質そのものを消し去るのではなく、それを十分な並列性と十分なインテリジェンスで囲い込み、システム全体から見たときにその性質が目立たなくなるようにしているのです。

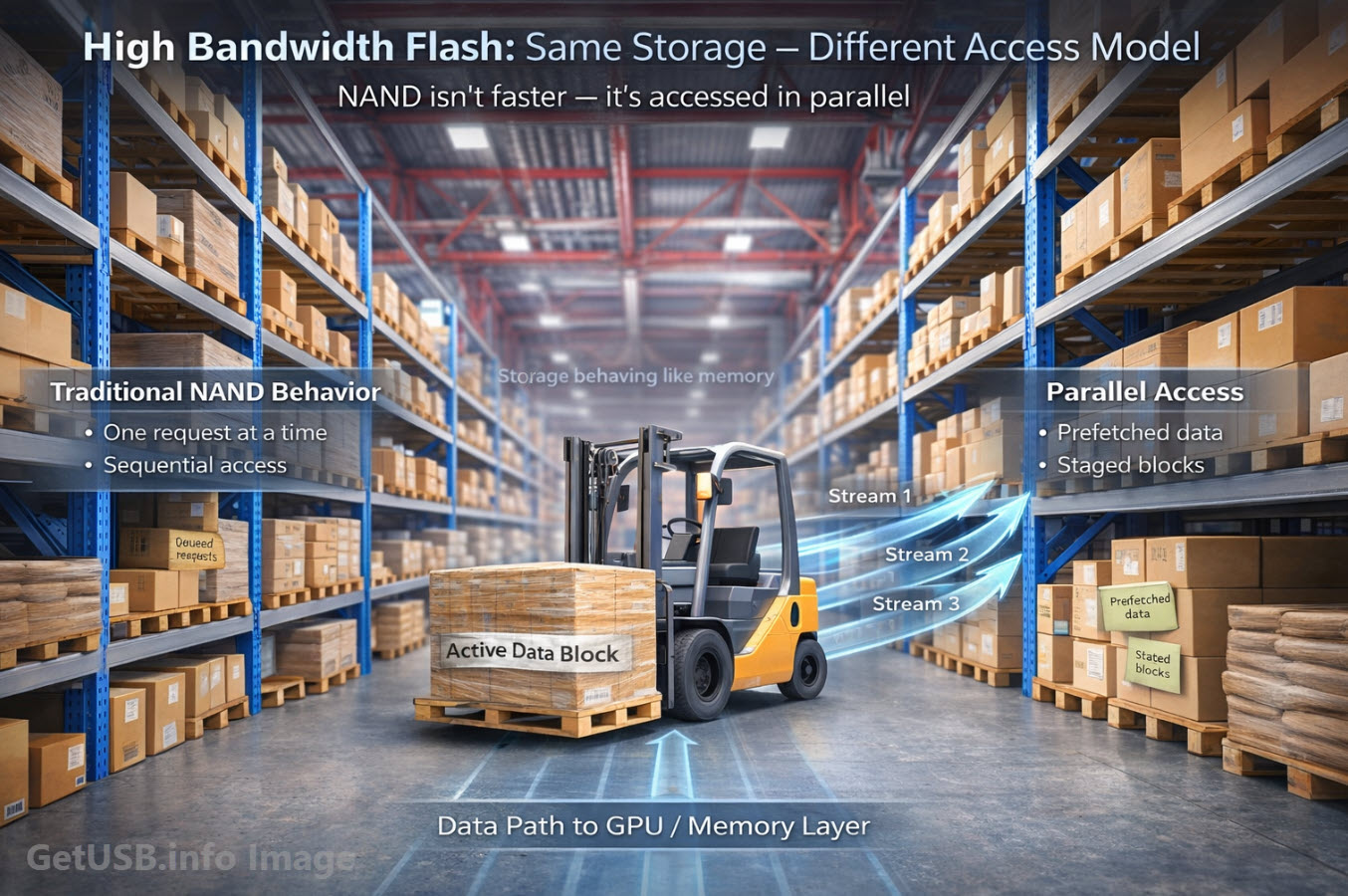

倉庫のたとえをもう少し広げると

前の記事で使った同じ倉庫のたとえを続けるなら、NANDはずっとメインの保管フロアでした。

あらゆるものがそこに置かれ、棚や列できれいに整理され、アクセス速度よりも密度と効率を重視して最適化されています。

DRAMは荷捌き場で、実際の作業が行われる場所です。SCMはそのすぐ後ろにあるステージングエリアです。

High Bandwidth Flashは、この倉庫の回し方を変えます。

以前は1人の作業員が通路に入って品物を1つずつ取っていたのが、今は複数の荷捌き場が同時に開き、何台ものフォークリフトが並列に動き、さらにシステムが次に必要としそうなものを先回りして配置しておくようになるのです。

倉庫そのものが根本から変わったわけではありませんが、アクセスのされ方は変わっています。

倉庫を荷捌き場そのものに変えているのではなく、倉庫がまるで荷捌き場のすぐそばにあるかのように振る舞わせているわけです。

実際にはどう構築されているのか

High Bandwidth Flashを可能にしている要素の多くは、NANDそのものから来ているわけではなく、その周囲の層から生まれています。

コントローラは今や、容量や摩耗管理だけでなく、複数のNANDダイやチャネルにまたがる並列動作をどうさばくかでより大きな役割を担っています。同時に、インターフェース帯域も拡大を続けており、バスに縛られずにデータを動かせる余地が増えています。

ただ、最も大きな違いを生んでいるのは、ソフトウェアがハードウェアとどう関わるかです。

データは、要求されてから取りに行くだけの存在ではなくなりました。予測され、前もって配置され、キャッシュされ、AIワークロードの振る舞いに合わせて整理されます。つまり、アクセスパターンを先読みし、よく使うデータをスタックの上位に近づけ、システムが遅い経路へ落ちる回数をできるだけ減らすということです。

もちろん、これでNANDが本物のメモリになるわけではありませんが、少なくとも以前よりはずっと積極的にメモリシステムへ参加できるようになります。

それでも、まだ違うもの

ここまで進歩しても、期待値は現実的に保っておく必要があります。

High Bandwidth Flashは、NANDをDRAMと同等にするものではありません。NANDは依然としてブロックベースであり、どんな本物のメモリよりも高い遅延を持ち、厳しい環境で高い性能を出すには依然としてコントローラとソフトウェアに大きく依存します。

そうした制約が消えるわけではなく、システム設計によってより上手に扱われるようになるだけです。

AIインフラの中でどこに収まるのか

実際の導入例では、High Bandwidth Flashは、巨大なデータセットを扱う必要がありながら、それらをすべて高価なメモリ階層へ押し込めないシステムの中で現れ始めています。

実際の姿を言えば、これはNANDを以前よりもずっと能動的に使うシステムです。単なる保存場所としてではなく、計算リソースへより連続的にデータを供給するワーキングデータ経路の一部としてNANDを使うのです。

たとえば大規模な推論環境では、モデルやコンテキストデータがDRAMに現実的に収まる量を超えることがよくあります。すべてを無理にメモリへ押し込むのではなく、高スループットでNANDへアクセスすることで、データが十分な速さで流れ込み、従来型ストレージというよりメモリの延長のように振る舞えるようになります。

トレーニング環境では、データセットが何度も再訪され、並列に処理され続けます。そのとき重要なのは、単発のバーストに対処することではなく、安定した流れを維持することです。High Bandwidth Flashは、複数のデータ経路を同時にアクティブに保つことで、どれか1つの要求がボトルネックになる可能性を下げます。

分散型のNVMe fabricシステムでも考え方は同じです。データは多くのデバイスやノードに分散されていますが、単純な保存容量ではなく、スループットと可用性を重視した形で協調的にアクセスされます。NANDが担う根本的な役割は変わりませんが、システムがそれと関わる方法は昔よりはるかに動的になっています。

その結果、NANDはスタック最下層の遠い層のようには感じられなくなり、たとえ完全にメモリの性能特性へ到達しなくても、アクティブなシステムの一部のように見え始めるのです。

なぜこの方向性が重要なのか

少し引いて、この3本の記事全体を眺めると、あるパターンが見えてきます。

HBMはメモリをコンピュートへ近づけ、SCMはメモリとストレージのあいだの溝を縮め、High Bandwidth Flashはストレージをメモリへ近づけます。

すべてが向かっている目標は同じです。データが移動しなければならない距離を減らし、システムが待たされる時間を減らすことです。

全体像に戻ると

NANDはなくなりません。

むしろ、こうしたシステムが必要とする総データ量は増え続けているのですから、重要性は高まっているとさえ言えます。

変わっているのは、NANDの使われ方です。

NANDはもう、スタック最下層の受け身な層ではありません。上へ引き上げられ、より密接に統合され、完全にそうなることはなくても、どんどんメモリに近い振る舞いを求められるようになっています。

この変化こそ、最初の記事で指摘したことでした。業界はNANDを置き換えたのではなく、NANDの周りを作り変えたのです。

次に来るもの

ここから先、スタックは上下両方向へ進化を続けます。

上ではメモリがさらに高速化し、より特化していきます。下ではストレージがより賢く、より統合されたものになっていきます。そしてその中間では、両者を分ける線がますます曖昧になっていきます。

次の記事では、AIシステムがリアルタイムでワーキングデータをどう扱っているのか、そしてコンテキストやKVキャッシュのような概念が、メモリとストレージを一緒に設計する方法へなぜ影響し始めているのかを見ていきます。

編集メモ

この記事の視点、方向性、そして技術的な framing は、本文全体で扱っているテーマと、AIインフラの中でNANDがメモリ層へ近づけられているというより広い議論を踏まえたうえで、著者によって定められました。

AIは、リズム、文の流れ、構成整理を補助する下書きアシスタントとして使われましたが、主題の方向付け、比較の観点、そして最終的な編集意図は著者によって決められています。

添付画像もAIで作成したものですが、ありきたりなストックビジュアルとしてではなく、通常の画像では伝えにくい記事固有の概念を表現するために用意した専用のイラストです。特に、現代のデータアーキテクチャの中でNANDフラッシュがメモリに隣接したアクティブな層のように振る舞う、という発想を可視化することを意図しています。

すべての内容は公開前に著者が確認し、調整し、承認しました。

Tags: AI storage architecture, high bandwidth flash, memory hierarchy, NAND memory, NVMe performance